## General specifications and features

Table 1 General

| Technical data                             | CPU 1212C<br>AC/DC/Relay      | CPU 1212C<br>DC/DC/Relay      | CPU 1212C<br>DC/DC/DC         |

|--------------------------------------------|-------------------------------|-------------------------------|-------------------------------|

| Order number                               | 6ES7 212-1BE31-0XB0           | 6ES7 212-1HE31-0XB0           | 6ES7 212-1AE31-0XB0           |

| Dimensions W x H x D (mm)                  | 90 x 100 x 75                 | 90 x 100 x 75                 | 90 x 100 x 75                 |

| Shipping weight                            | 425 grams                     | 385 grams                     | 370 grams                     |

| Power dissipation                          | 11 W                          | 9 W                           | 9 W                           |

| Current available<br>(SM and CM bus)       | 1000 mA max.<br>(5 VDC)       | 1000 mA max.<br>(5 VDC)       | 1000 mA max.<br>(5 VDC)       |

| Current available (24 VDC)                 | 300 mA max.<br>(sensor power) | 300 mA max.<br>(sensor power) | 300 mA max.<br>(sensor power) |

| Digital input current consumption (24 VDC) | 4 mA/input used               | 4 mA/input used               | 4 mA/input used               |

Table 2 CPU features

| Technical data                                                    |                 | Description                                                                                                                                                                                                                                                                       |  |

|-------------------------------------------------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| User memory <sup>1</sup>                                          | Work            | 50 Kbytes                                                                                                                                                                                                                                                                         |  |

|                                                                   | Load            | 1 Mbyte internal, expandable up to SD card size                                                                                                                                                                                                                                   |  |

|                                                                   | Retentive       | 10 Kbytes                                                                                                                                                                                                                                                                         |  |

| On-board digital I/                                               | 0               | 8 inputs/6 outputs                                                                                                                                                                                                                                                                |  |

| On-board analog I                                                 | /O              | 2 inputs                                                                                                                                                                                                                                                                          |  |

| Process image siz                                                 | e               | 1024 bytes of inputs (I)/1024 bytes of outputs (Q)                                                                                                                                                                                                                                |  |

| Bit memory (M)                                                    |                 | 4096 bytes                                                                                                                                                                                                                                                                        |  |

| Temporary (local)                                                 | memory          | <ul> <li>16 Kbytes for startup and program cycle (including associated FBs and FCs)</li> <li>4 Kbytes for standard interrupt events including FBs and FCs</li> <li>4 Kbytes for error interrupt events including FBs and FCs</li> </ul>                                           |  |

| Signal modules ex                                                 | pansion         | 2 SMs max.                                                                                                                                                                                                                                                                        |  |

| SB, CB, BB expan                                                  | sion            | 1 max.                                                                                                                                                                                                                                                                            |  |

| Communication m                                                   | odule expansion | 3 CMs max.                                                                                                                                                                                                                                                                        |  |

| Single phase: 3 at 100 kHz and 1 at 30 kHz clock rate, SB: 2 at 3 |                 | <ul> <li>5 built in I/O, 6 with signal board, see table, <u>HSC input assignments for CPU 1212C</u></li> <li>Single phase: 3 at 100 kHz and 1 at 30 kHz clock rate, SB: 2 at 30 kHz</li> <li>Quadrature phase: 3 at 80 kHz and 1 at 20 kHz clock rate, SB: 2 at 20 kHz</li> </ul> |  |

| Pulse outputs <sup>2</sup>                                        |                 | 4                                                                                                                                                                                                                                                                                 |  |

| Pulse catch inputs                                                |                 | 8                                                                                                                                                                                                                                                                                 |  |

This document constitutes a free excerpt compiled by the user himself/herself from the documentation provided by Siemens for this product. Siemens disclaims all liability for the completeness of this document. It shall only be used for the user's own internal purposes. It shall not be passed on to third parties. The complete documentation can be found at:

#### General specifications and features

| Technical data                 | Description                                                          |

|--------------------------------|----------------------------------------------------------------------|

| Time delay / cyclic interrupts | 4 total with 1 ms resolution                                         |

| Edge interrupts                | 8 rising and 8 falling (12 and 12 with optional signal board)        |

| Memory card                    | SIMATIC Memory Card (optional)                                       |

| Real time clock accuracy       | +/- 60 seconds/month                                                 |

| Real time clock retention time | 20 days typ./12 days min. at 40°C (maintenance-free Super Capacitor) |

<sup>&</sup>lt;sup>1</sup> The size of the user program, data, and configuration is limited by the available load memory and work memory in the CPU. There is no specific limit to the number of OB, FC, FB and DB blocks supported or to the size of a particular block; the only limit is due to overall memory size.

Table 3 Performance

| Type of instruction | Execution speed     |

|---------------------|---------------------|

| Boolean             | 0.08 μs/instruction |

| Move Word           | 1.7 µs/instruction  |

| Real math           | 2.3 µs/instruction  |

<sup>&</sup>lt;sup>2</sup> For CPU models with relay outputs, you must install a digital signal board (SB) to use the pulse outputs.

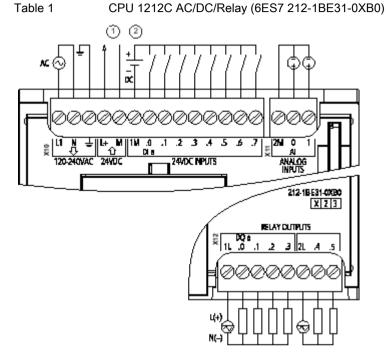

#### **CPU 1212C Wiring diagrams**

- ① 24 VDC Sensor Power Out

- For additional noise immunity, connect "M" to chassis ground even if not using sensor supply.

- ② For sinking inputs, connect "-" to "M" (shown). For sourcing inputs, connect "+" to "M".

Note: X11 connectors must be gold. See Appendix C, Spare Parts for order number.

Table 2 Connector pin locations for CPU 1212C AC/DC/Relay (6ES7 212-1BE31-0XB0)

| Pin | X10                   | X11 (gold) | X12    |

|-----|-----------------------|------------|--------|

| 1   | L1 / 120-240 VAC      | 2 M        | 1L     |

| 2   | N / 120-240 VAC       | AI 0       | DQ a.0 |

| 3   | Functional Earth      | Al 1       | DQ a.1 |

| 4   | L+ / 24VDC Sensor Out |            | DQ a.2 |

| 5   | M / 24VDC Sensor Out  |            | DQ a.3 |

| 6   | 1M                    |            | 2L     |

| 7   | DI a.0                |            | DQ a.4 |

| 8   | DI a.1                |            | DQ a.5 |

| 9   | DI a.2                |            |        |

| 10  | DI a.3                |            |        |

| 11  | DI a.4                |            |        |

| 12  | DI a.5                |            |        |

| 13  | DI a.6                |            |        |

| 14  | DI a.7                |            |        |

This document constitutes a free excerpt compiled by the user himself/herself from the documentation provided by Siemens for this product. Siemens disclaims all liability for the completeness of this document. It shall only be used for the user's own internal purposes. It shall not be passed on to third parties. The complete documentation can be found at:

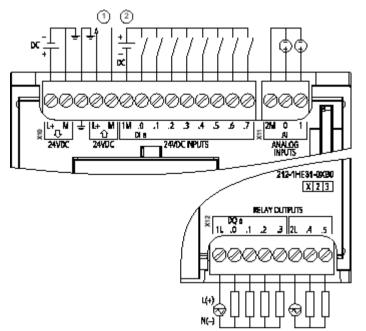

Table 3 CPU 1212C DC/DC/Relay (6ES7 212-1HE31-0XB0)

24 VDC Sensor Power Out

For additional noise immunity, connect "M" to chassis ground even if

not using sensor supply.

② For sinking inputs, connect "-" to "M" (shown). For sourcing inputs, connect "+" to "M".

Note: X11 connectors must be gold. See Appendix C, Spare Parts for order number.

Table 4 Connector pin locations for CPU 1212C DC/DC/Relay (6ES7 212-1HE31-0XB0)

| Pin | X10                   | X11 (gold) | X12    |

|-----|-----------------------|------------|--------|

| 1   | L+ / 24VDC            | 2 M        | 1L     |

| 2   | M / 24VDC             | AI 0       | DQ a.0 |

| 3   | Functional Earth      | Al 1       | DQ a.1 |

| 4   | L+ / 24VDC Sensor Out |            | DQ a.2 |

| 5   | M / 24VDC Sensor Out  |            | DQ a.3 |

| 6   | 1M                    |            | 2L     |

| 7   | DI a.0                |            | DQ a.4 |

| 8   | DI a.1                |            | DQ a.5 |

| 9   | DI a.2                |            |        |

| 10  | DI a.3                |            |        |

| 11  | DI a.4                |            |        |

| 12  | DI a.5                |            |        |

| 13  | DI a.6                |            |        |

| 14  | DI a.7                |            |        |

This document constitutes a free excerpt compiled by the user himself/herself from the documentation provided by Siemens for this product. Siemens disclaims all liability for the completeness of this document. It shall only be used for the user's own internal purposes. It shall not be passed on to third parties. The complete documentation can be found at:

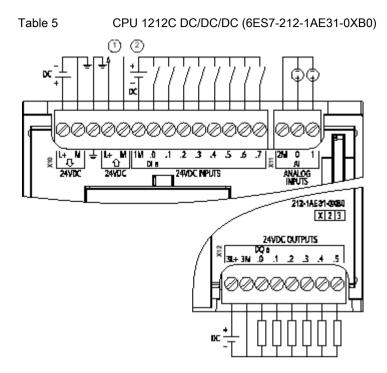

- 24 VDC Sensor Power Out

For additional noise immunity, connect "M" to chassis ground even if not using sensor supply.

- ② For sinking inputs, connect "-" to "M" (shown).

For sourcing inputs, connect "+" to "M".

Note: X11 connectors must be gold. See Appendix C, Spare Parts for order number.

Table 6 Connector pin locations for CPU 1212C DC/DC/DC (6ES7 212-1AE31-0XB0)

| Pin | X10                   | X11 (gold) | X12    |

|-----|-----------------------|------------|--------|

| 1   | L+ / 24VDC            | 2 M        | 3L+    |

| 2   | M / 24VDC             | AI 0       | 3M     |

| 3   | Functional Earth      | Al 1       | DQ a.0 |

| 4   | L+ / 24VDC Sensor Out |            | DQ a.1 |

| 5   | M / 24VDC Sensor Out  |            | DQ a.2 |

| 6   | 1M                    |            | DQ a.3 |

| 7   | DI a.0                |            | DQ a.4 |

| 8   | DI a.1                |            | DQ a.5 |

| 9   | DI a.2                |            |        |

| 10  | DI a.3                |            |        |

| 11  | DI a.4                |            |        |

| 12  | DI a.5                |            |        |

| 13  | DI a.6                |            |        |

| 14  | DI a.7                |            |        |

## Sample time for the built-in analog ports of the CPU

Table 1 Sample time for built-in analog inputs of the CPU

| Rejection frequency (Integration time selection) | Sample time |

|--------------------------------------------------|-------------|

| 60 Hz (16.6 ms)                                  | 4.17 ms     |

| 50 Hz (20 ms)                                    | 5 ms        |

| 10 Hz (100 ms)                                   | 25 ms       |

## Step response of the built-in analog inputs of the CPU

Table 1 Step Response (ms), 0V to 10V measured at 95%

| Smoothing selection (sample averaging) | Rejection frequency (Integration time) |        |         |

|----------------------------------------|----------------------------------------|--------|---------|

|                                        | 60 Hz                                  | 50 Hz  | 10 Hz   |

| None (1 cycle): No averaging           | 50 ms                                  | 50 ms  | 100 ms  |

| Weak (4 cycles): 4 samples             | 60ms                                   | 70 ms  | 200 ms  |

| Medium (16 cycles): 16 samples         | 200 ms                                 | 240 ms | 1150 ms |

| Strong (32 cycles): 32 samples         | 400 ms                                 | 480 ms | 2300 ms |

| Sample time                            | 4.17 ms                                | 5 ms   | 25 ms   |

## **Analog inputs**

Table 1 Analog inputs

| Description                                                            |

|------------------------------------------------------------------------|

| 2                                                                      |

| Voltage (single-ended)                                                 |

| 0 to 10 V                                                              |

| 0 to 27648                                                             |

| 10.001 to 11.759 V                                                     |

| 27,649 to 32,511                                                       |

| 11.760 to 11.852 V                                                     |

| 32,512 to 32,767                                                       |

| 10 bits                                                                |

| 35 VDC                                                                 |

| None, Weak, Medium, or Strong                                          |

| See the table for step response (ms) for the analog inputs of the CPU. |

| 10, 50, or 60 Hz                                                       |

| ≥100 KΩ                                                                |

| None                                                                   |

| 3.0% / 3.5% of full-scale                                              |

| 100 m, shielded twisted pair                                           |

|                                                                        |

# Digital inputs and outputs

Table 1 Digital inputs

| Technical data                                                 | CPU 1212C AC/DC/Relay, DC/DC/Relay, and DC/DC/DC                                                                                    |

|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| Number of inputs                                               | 8                                                                                                                                   |

| Туре                                                           | Sink/Source (IEC Type 1 sink)                                                                                                       |

| Rated voltage                                                  | 24 VDC at 4 mA, nominal                                                                                                             |

| Continuous permissible voltage                                 | 30 VDC, max.                                                                                                                        |

| Surge voltage                                                  | 35 VDC for 0.5 sec.                                                                                                                 |

| Logic 1 signal (min.)                                          | 15 VDC at 2.5 mA                                                                                                                    |

| Logic 0 signal (max.)                                          | 5 VDC at 1 mA                                                                                                                       |

| Isolation (field side to logic)                                | 500 VAC for 1 minute                                                                                                                |

| Isolation groups                                               | 1                                                                                                                                   |

| Filter times                                                   | 0.2, 0.4, 0.8, 1.6, 3.2, 6.4, and 12.8 ms (selectable in groups of 4)                                                               |

| HSC clock input rates (max.)<br>(Logic 1 Level = 15 to 26 VDC) | Single phase: 100 KHz (la.0 to la.5) and 30 KHz (la.6 to la.7)<br>Quadrature phase: 80 KHz (la.0 to la.5) and 20 KHz (la.6 to la.7) |

| Number of inputs on simultaneously                             | 8 at 60°C horizontal, 50°C vertical                                                                                                 |

| Cable length (meters)                                          | 500 m shielded, 300 m unshielded, 50 m shielded for HSC inputs                                                                      |

Table 2 Digital outputs

| Technical data                  | CPU 1212C AC/DC/Relay and DC/DC/Relay                        | CPU 1212C<br>DC/DC/DC           |  |

|---------------------------------|--------------------------------------------------------------|---------------------------------|--|

| Number of outputs               | 6                                                            | 6                               |  |

| Туре                            | Relay, dry contact                                           | Solid state - MOSFET (sourcing) |  |

| Voltage range                   | 5 to 30 VDC or 5 to 250 VAC                                  | 20.4 to 28.8 VDC                |  |

| Logic 1 signal at max. current  |                                                              | 20 VDC min.                     |  |

| Logic 0 signal with 10 KΩ load  |                                                              | 0.1 VDC max.                    |  |

| Current (max.)                  | 2.0 A                                                        | 0.5 A                           |  |

| Lamp load                       | 30 W DC / 200 W AC                                           | 5 W                             |  |

| ON state resistance             | 0.2 Ω max. when new                                          | 0.6 Ω max.                      |  |

| Leakage current per point       |                                                              | 10 μA max.                      |  |

| Surge current                   | 7 A with contacts closed                                     | 8 A for 100 ms max.             |  |

| Overload protection             | No                                                           | No                              |  |

| Isolation (field side to logic) | 1500 VAC for 1 minute (coil to contact) None (coil to logic) | 500 VAC for 1 minute            |  |

This document constitutes a free excerpt compiled by the user himself/herself from the documentation provided by Siemens for this product. Siemens disclaims all liability for the completeness of this document. It shall only be used for the user's own internal purposes. It shall not be passed on to third parties. The complete documentation can be found at:

#### Digital inputs and outputs

| Technical data                          | CPU 1212C AC/DC/Relay<br>and DC/DC/Relay         | CPU 1212C<br>DC/DC/DC                            |

|-----------------------------------------|--------------------------------------------------|--------------------------------------------------|

| Isolation resistance                    | 100 MΩ min. when new                             |                                                  |

| Isolation between open contacts         | 750 VAC for 1 minute                             |                                                  |

| Isolation groups                        | 2                                                | 1                                                |

| Inductive clamp voltage                 |                                                  | L+ minus 48 VDC, 1 W dissipation                 |

| Switching delay (Qa.0 to Qa.3)          | 10 ms max.                                       | 1.0 µs max., off to on 3.0 µs max., on to off    |

| Switching delay (Qa.4 to Qa.5)          | 10 ms max.                                       | 50 μs max., off to on<br>200 μs max., on to off  |

| Maximum relay switching frequency       | 1 Hz                                             |                                                  |

| Pulse Train Output rate (Qa.0 and Qa.2) | Not recommended <sup>1</sup>                     | 100 KHz max.,<br>2 Hz min. <sup>2</sup>          |

| Lifetime mechanical (no load)           | 10,000,000 open/close cycles                     |                                                  |

| Lifetime contacts at rated load         | 100,000 open/close cycles                        |                                                  |

| Behavior on RUN to STOP                 | Last value or substitute value (default value 0) | Last value or substitute value (default value 0) |

| Number of outputs on simultaneously     | 6 up to 60°C horizontal, 50°C vertical           |                                                  |

| Cable length (meters)                   | 500 m shielded,<br>150 m unshielded              | 500 m shielded,<br>150 m unshielded              |

<sup>&</sup>lt;sup>1</sup> For CPU models with relay outputs, you must install a digital signal board (SB) to use the pulse outputs.

<sup>&</sup>lt;sup>2</sup> Depending on your pulse receiver and cable, an additional load resistor (at least 10% of rated current) may improve pulse signal quality and noise immunity.

#### Timers, counters and code blocks supported by CPU 1212C

Table 1 Blocks, timers and counters supported by CPU 1212C

| Element  |                                             | Description                                                                                                                                                                                    |  |

|----------|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Blocks   | Туре                                        | OB, FB, FC, DB                                                                                                                                                                                 |  |

|          | Size                                        | 50 Kbytes                                                                                                                                                                                      |  |

|          | Quantity                                    | Up to 1024 blocks total (OBs + FBs + FCs + DBs)                                                                                                                                                |  |

|          | Address range for FBs, FCs, and DBs         | 1 to 65535 (such as FB 1 to FB 65535)                                                                                                                                                          |  |

|          | Nesting depth                               | 16 from the program cycle or start up OB; 4 from the time delay interrupt, time-of-day interrupt, cyclic interrupt, hardware interrupt, time error interrupt, or diagnostic error interrupt OB |  |

|          | Monitoring                                  | Status of 2 code blocks can be monitored simultaneously                                                                                                                                        |  |

| OBs      | Program cycle                               | Multiple: OB 1, OB 200 to OB 65535                                                                                                                                                             |  |

|          | Startup                                     | Multiple: OB 100, OB 200 to OB 65535                                                                                                                                                           |  |

|          | Time-delay interrupts and cyclic interrupts | 4 <sup>1</sup> (1 per event): OB 200 to OB 65535                                                                                                                                               |  |

|          | Hardware interrupts (edges and HSC)         | 50 (1 per event): OB 200 to OB 65535                                                                                                                                                           |  |

|          | Time error interrupts                       | 1: OB 80                                                                                                                                                                                       |  |

|          | Diagnostic error interrupts                 | 1: OB 82                                                                                                                                                                                       |  |

| Timers   | Туре                                        | IEC                                                                                                                                                                                            |  |

|          | Quantity                                    | Limited only by memory size                                                                                                                                                                    |  |

|          | Storage                                     | Structure in DB, 16 bytes per timer                                                                                                                                                            |  |

| Counters | Туре                                        | IEC                                                                                                                                                                                            |  |

|          | Quantity                                    | Limited only by memory size                                                                                                                                                                    |  |

|          | Storage                                     | Structure in DB, size dependent upon count type  SInt, USInt: 3 bytes  Int, UInt: 6 bytes  DInt, UDInt: 12 bytes                                                                               |  |

<sup>&</sup>lt;sup>1</sup> Time-delay and cyclic interrupts use the same resources in the CPU. You can have only a total of 4 of these interrupts (time-delay plus cyclic interrupts). You cannot have 4 time-delay interrupts and 4 cyclic interrupts.

Table 2 Communication

| Technical data  | Description |

|-----------------|-------------|

| Number of ports | 1           |

Timers, counters and code blocks supported by CPU 1212C

| Technical data                           | Description                                                                                                                               |  |

|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|

| Туре                                     | Ethernet                                                                                                                                  |  |

| HMI device <sup>1</sup>                  | 3                                                                                                                                         |  |

| Programming device (PG)                  | 1                                                                                                                                         |  |

| Connections                              | 8 for Open User Communication (active or passive): TSEND_C, TRCV_C, TCON, TDISCON, TSEND, and TRCV      CETTRUT (ORL) ORL) ORL (ORL) ORL) |  |

|                                          | <ul> <li>3 for server GET/PUT (CPU-to-CPU) S7 communication</li> <li>8 for client GET/PUT (CPU-to-CPU) S7 communication</li> </ul>        |  |

| Data rates                               | 10/100 Mb/s                                                                                                                               |  |

| Isolation (external signal to PLC logic) | Transformer isolated, 1500 VAC, for short term event safety only                                                                          |  |

| Cable type                               | CAT5e shielded                                                                                                                            |  |

<sup>&</sup>lt;sup>1</sup> The CPU provides dedicated HMI connections to support up to 3 HMI devices. (You can have up to 2 SIMATIC Comfort panels.) The total number of HMI is affected by the types of HMI panels in your configuration. For example, you could have up to three SIMATIC Basic panels connected to your CPU, or you could have up to two SIMATIC Comfort panels with one additional Basic panel.

Table 3 Power supply

| Technical data                              |                                    | CPU 1212C<br>AC/DC/Relay               | CPU 1212C<br>DC/DC/Relay                                                             | CPU 1212C<br>DC/DC/DC |

|---------------------------------------------|------------------------------------|----------------------------------------|--------------------------------------------------------------------------------------|-----------------------|

| Voltage range                               |                                    | 85 to 264 VAC                          | 20.4 VDC to 28.8 VDC<br>22.0 VDC to 28.8 VDC for ambient temperature<br>-20° to 0° C |                       |

| Line frequency                              |                                    | 47 to 63 Hz                            |                                                                                      |                       |

| Input current (max. load)                   | CPU only                           | 80 mA at 120 VAC<br>40 mA at 240 VAC   | 400 mA at 24 VDC                                                                     | 400 mA at 24 VDC      |

|                                             | CPU with all expansion accessories | 240 mA at 120 VAC<br>120 mA at 240 VAC | 1200 mA at 24 VDC                                                                    | 1200 mA at 24 VDC     |

| Inrush current (max.)                       |                                    | 20 A at 264 VAC                        | 12 A at 28.8 VDC                                                                     | 12 A at 28.8 VDC      |

| Isolation (input power to logic)            |                                    | 1500 VAC                               | Not isolated                                                                         | Not isolated          |

| Ground leakage, AC line to functional earth |                                    | 0.5 mA max.                            |                                                                                      |                       |

| Hold up time (loss of power)                |                                    | 20 ms at 120 VAC<br>80 ms at 240 VAC   | 10 ms at 24 VDC                                                                      | 10 ms at 24 VDC       |

| Internal fuse, not u                        | user replaceable                   | 3 A, 250 V, slow blow                  | 3 A, 250 V, slow blow                                                                | 3 A, 250 V, slow blow |

This document constitutes a free excerpt compiled by the user himself/herself from the documentation provided by Siemens for this product. Siemens disclaims all liability for the completeness of this document. It shall only be used for the user's own internal purposes. It shall not be passed on to third parties. The complete documentation can be found at:

Table 4 Sensor power

| Technical data                        | CPU 1212C<br>AC/DC/Relay         | CPU 1212C<br>DC/DC/Relay                                   | CPU 1212C<br>DC/DC/DC            |

|---------------------------------------|----------------------------------|------------------------------------------------------------|----------------------------------|

| Voltage range                         | 20.4 to 28.8 VDC                 | L+ minus 4 VDC min.                                        |                                  |

|                                       |                                  | L+ minus 5 VDC min. for ambient temperature -20° C to 0° C |                                  |

| Output current rating (max.)          | 300 mA (short circuit protected) | 300 mA (short circuit protected)                           | 300 mA (short circuit protected) |

| Maximum ripple noise (<10 MHz)        | < 1 V peak to peak               | Same as input line                                         | Same as input line               |

| Isolation (CPU logic to sensor power) | Not isolated                     | Not isolated                                               | Not isolated                     |